# **Product Specification**

Supplier:GoldenMorning Electronic

Model Number: GME12864-12

| PREPARED BY | CHECKED BY | APPROVED BY |

|-------------|------------|-------------|

|             |            |             |

# GME12864-12

### **CUSTOMER P/N:**

| VERSION NO. | CHANGE DESCRIPTION            | DATE       |

|-------------|-------------------------------|------------|

| 0           | ORIGINAL VERSION              | 2014/08/20 |

| 1           | DRIVER IC CHANGED TO SSD1306B | 2023/10/20 |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

|             |                               |            |

PREPARED BY: Xie Yaping DATE: <u>20 2 3 / 1 0</u> /20

APPROVED BY: Cheng Xiaojun DATE: 20 2 3 / 1 0 /20

# **CONTENTS**

| 1. FUNCTIONS & FEATURES 2                                        | )        |

|------------------------------------------------------------------|----------|

| 2. MECHANICAL SPECIFICATIONS2                                    | )        |

| 3. EXTERNAL DIMENSIONS ( unit: mm) 3                             | <b>,</b> |

| 4. BLOCK DIAGRAM······· 4                                        | ļ        |

| 5. PIN ASSIGNMENT 4                                              | ļ        |

| 6. ABSOLUTE MAXIMUM RATINGS 5                                    | ;        |

| 7. ELECTRICAL CHARACTERISTICS 5                                  | ;        |

| 8. COMMANDS 8                                                    | ;        |

| 9. FUNCTIONAL SPECIFICATION ···································· | 2        |

| 10. MODULE ACCEPT QUALITY LEVEL (AQL)1                           | 4        |

| 11. RELIABILITY TEST1                                            | .5       |

| 12. OHALITY DESCRIPTION & APPLICTION NOTE                        | 5        |

### 1. FUNCTIONS & FEATURES

### • LCD TYPE:

| MODULE MODEL | LCD TYPE                       | REMARK |

|--------------|--------------------------------|--------|

| GME12864-12  | 0.96" OLED Passive Matrix Blue |        |

Driving Scheme : 1/64 Duty,

Viewing direction : 6 O'clock

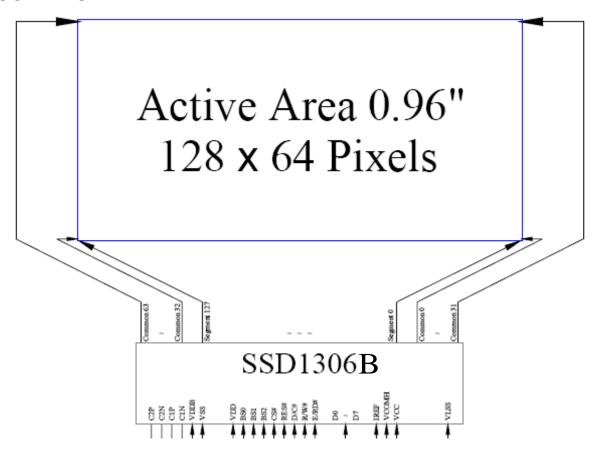

Drive IC : SSD1306B

Power Supply Voltage : 3.0V

V<sub>CC</sub> : 12.0V

Interface : IIC

RoHS Compliant

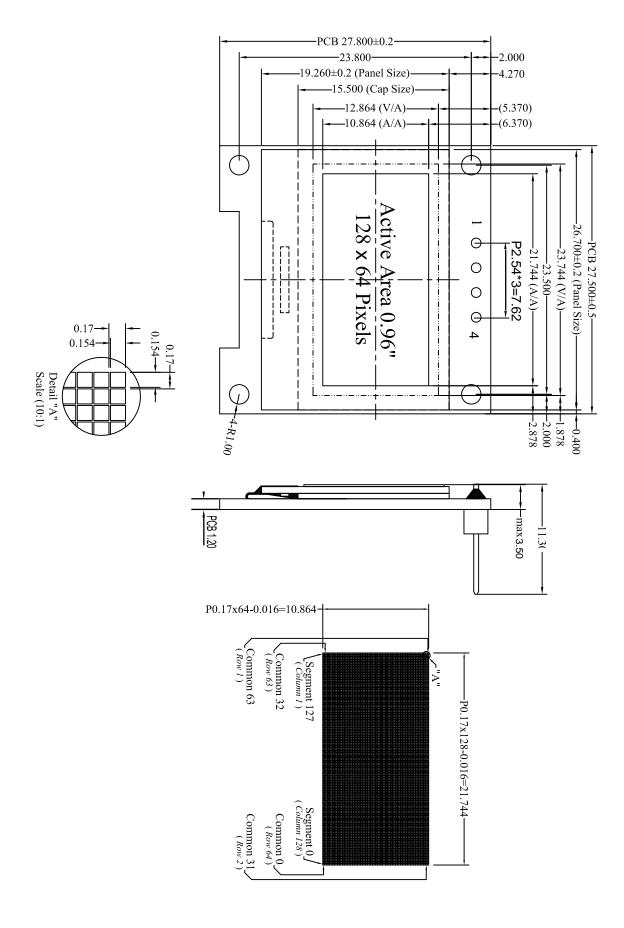

### 2. MECHANICAL SPECIFICATIONS

• Module Size : 27.50 (L) x27.80 (W) x3.50Max (T) mm

Viewing Area

∴ 23.744(L) x 12.864 (W) mm

Active Area

∴ 21.744 (L) x 10.864 (W) mm

Dot Pitch

∴ 0.154 (W) x 0.154 (H) mm

Dot Size

∴ 0.17(W) x 0.17(H) mm

## 3. EXTERNAL DIMENSIONS (⊕ unit: mm)

### 4. BLOCK DIAGRAM

### **5. PIN ASSIGNMENT**

| PIN | SYMBOL | Descriptions            |  |  |  |  |  |  |  |  |

|-----|--------|-------------------------|--|--|--|--|--|--|--|--|

| 1   | GND    | Ground of Logic Circuit |  |  |  |  |  |  |  |  |

| 2   | VDD    | Power Supply for Logic  |  |  |  |  |  |  |  |  |

| 3   | SCK    | Serial clock input.     |  |  |  |  |  |  |  |  |

| 4   | SDA    | Serial data input.      |  |  |  |  |  |  |  |  |

### 6. ABSOLUTE MAXIMUM RATINGS

| Parameter                  | Symbol           | Min    | Max | Unit | Notes |

|----------------------------|------------------|--------|-----|------|-------|

| Supply Voltage for Logic   | $V_{DD}$         | -0.3   | 4   | V    | 1, 2  |

| Supply Voltage for Display | V <sub>cc</sub>  | 0      | 16  | V    | 1, 2  |

| Supply Voltage for DC/DC   | V <sub>BAT</sub> | -0.3   | 5   | V    | 1, 2  |

| Operating Temperature      | T <sub>OP</sub>  | -40    | 85  | °C   |       |

| Storage Temperature        | T <sub>STG</sub> | -40    | 85  | °C   | 3     |

| Life Time (120 cd/m²)      |                  | 10,000 | -   | hour | 4     |

| Life Time (80 cd/m²)       |                  | 30,000 | -   | hour | 4     |

| Life Time (60 cd/m²)       |                  | 50,000 | -   | hour | 4     |

Note 1: All the above voltages are on the basis of " $V_{SS} = 0V$ ".

Note 2: When this module is used beyond the above absolute maximum ratings, permanent breakage of the module may occur. Also, for normal operations, it is desirable to use this module under the conditions according to Section 3. "Optics & Electrical Characteristics". If this module is used beyond these conditions, malfunctioning of the module can occur and the reliability of the module may deteriorate.

Note 3: The defined temperature ranges do not include the polarizer. The maximum withstood temperature of the polarizer should be 80°C.

Note 4:  $V_{CC}$  = 12.0V,  $T_a$  = 25°C, 50% Checkerboard.

Software configuration follows Section 4.4 Initialization.

End of lifetime is specified as 50% of initial brightness reached. The average operating lifetime at room temperature is estimated by the accelerated operation at high temperature conditions.

### 7. ELECTRICAL CHARACTERISTICS

### 7.1. Optics Characteristics

| Characteristics                                             | Symbol          | Conditions  | Min          | Тур          | Max          | Unit   |

|-------------------------------------------------------------|-----------------|-------------|--------------|--------------|--------------|--------|

| Brightness<br>(V <sub>cc</sub> Supplied Externally)         | L <sub>br</sub> | Note 5      | 80           | 100          | -            | cd/m²  |

| Brightness<br>(V <sub>CC</sub> Generated by Internal DC/DC) | L <sub>br</sub> | Note 6      | 50           | 60           | -            | cd/m²  |

| C.I.E. (Blue)                                               | (x)<br>(y)      | C.I.E. 1931 | 0.10<br>0.20 | 0.14<br>0.24 | 0.18<br>0.28 |        |

| C.I.E. (Yellow)                                             | (x)<br>(y)      | C.I.E. 1931 | 0.43<br>0.45 | 0.47<br>0.49 | 0.51<br>0.53 |        |

| Dark Room Contrast                                          | CR              |             | -            | 2000:1       | -            |        |

| Viewing Angle                                               |                 |             | -            | Free         | -            | degree |

<sup>\*</sup> Optical measurement taken at  $V_{DD}$  = 2.8V,  $V_{CC}$  = 12V & 7.25V. Software configuration follows Section 4.4 Initialization.

### 7.2. DC CHARACTERISTICS

| Characteristics                                                              | Symbol                 | Conditions                         | Min                 | Тур  | Max                 | Unit |

|------------------------------------------------------------------------------|------------------------|------------------------------------|---------------------|------|---------------------|------|

| Supply Voltage for Logic                                                     | $V_{DD}$               |                                    | 1.65                | 2.8  | 3.3                 | ٧    |

| Supply Voltage for Display<br>(Supplied Externally)                          | Vα                     | Note 5<br>(Internal DC/DC Disable) | 11.5                | 12.0 | 12.5                | v    |

| Supply Voltage for DC/DC                                                     | $V_{zar}$              | Internal DC/DC Enable              | 3.5                 | -    | 4.2                 | ν    |

| Supply Voltage for Display<br>(Generated by Internal DC/DC)                  | Vcc                    | Note 6<br>(Internal DC/DC Enable)  | 7.0                 | -    | 7.5                 | ν    |

| High Level Input                                                             | $V_{\text{IH}}$        | I <sub>OUT</sub> = 100μA, 3.3MHz   | $0.8 \times V_{DD}$ | -    | $V_{DD}$            | V    |

| Low Level Input                                                              | V <sub>IL</sub>        | I <sub>OUT</sub> = 100μA, 3.3MHz   | 0                   | -    | 0.2×V <sub>DD</sub> | v    |

| High Level Output                                                            | V <sub>OH</sub>        | I <sub>OUT</sub> = 100μA, 3.3MHz   | 0.9×V <sub>DD</sub> | -    | V <sub>DD</sub>     | V    |

| Low Level Output                                                             | V <sub>OL</sub>        | I <sub>OUT</sub> = 100μA, 3.3MHz   | 0                   | -    | 0.1×V <sub>DD</sub> | v    |

| Operating Current for V <sub>DD</sub>                                        | I <sub>DD</sub>        |                                    | -                   | 180  | 300                 | μΑ   |

| Operating Current for V <sub>∞</sub><br>(V <sub>∞</sub> Supplied Externally) | I <sub>CC</sub>        | Note 7                             | -                   | 12.3 | 16                  | mA   |

| Operating Current for $V_{SUT}$<br>( $V_{CC}$ Generated by Internal DC/DC)   | $I_{	extit{	iny MT}}$  | Note 8                             | -                   | 21   | 28.0                | mΑ   |

| Sleep Mode Current for V <sub>DD</sub>                                       | I <sub>DD, SLEEP</sub> |                                    | -                   | 1    | 5                   | μΑ   |

| Sleep Mode Current for V <sub>CC</sub>                                       | I <sub>CC, SLEEP</sub> |                                    |                     | 2    | 10                  | μΑ   |

Note 5 & 6: Brightness (L<sub>br</sub>) and Supply Voltage for Display (V<sub>CC</sub>) are subject to the change of the panel characteristics and the customer's request.

Note 7:  $V_{DD} = 2.8V$ ,  $V_{CC} = 12V$ , 100% Display Area Turn on. Note 8:  $V_{DD} = 2.8V$ ,  $V_{CC} = 7.25V$ , 100% Display Area Turn on.

<sup>\*</sup> Software configuration follows Section 4.4 Initialization.

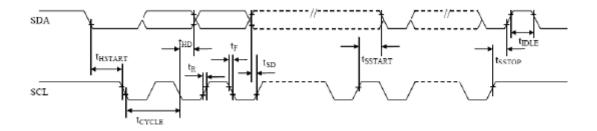

### 7.3.AC CHARACTERISTICS

### 1 I<sup>2</sup>C Interface Timing Characteristics:

| Symbol              | Description                                                                  | Min | Max | Unit |

|---------------------|------------------------------------------------------------------------------|-----|-----|------|

| t <sub>cycle</sub>  | Clock Cycle Time                                                             | 2.5 | -   | μs   |

| t <sub>HSTART</sub> | Start Condition Hold Time                                                    | 0.6 | -   | μs   |

|                     | Data Hold Time (for "SDA <sub>OUT</sub> " Pin)                               | 0   |     |      |

| t <sub>HD</sub>     | Data Hold Time (for "SDA <sub>IN</sub> " Pin)                                | 300 | -   | ns   |

| t <sub>SD</sub>     | Data Setup Time                                                              | 100 | -   | ns   |

| t <sub>SSTART</sub> | Start Condition Setup Time<br>(Only relevant for a repeated Start condition) | 0.6 | -   | μs   |

| t <sub>SSTOP</sub>  | Stop Condition Setup Time                                                    | 0.6 | -   | μs   |

| t <sub>R</sub>      | Rise Time for Data and Clock Pin                                             |     | 300 | ns   |

| t <sub>F</sub>      | Fall Time for Data and Clock Pin                                             |     | 300 | ns   |

| t <sub>IDLE</sub>   | Idle Time before a New Transmission can Start                                | 1.3 | -   | μs   |

<sup>\* (</sup>V<sub>DD</sub> - V<sub>SS</sub> = 1.65V to 3.3V, T<sub>a</sub> = 25°C)

### 8. COMMANDS

(D/C#=0, R/W#(WR#) = 0, E(RD#=1) unless specific setting is stated)

| 1. Fu | ndame  | ntal (     | Comm           | and T | able           |                |       |    |                |                      |                                                        |

|-------|--------|------------|----------------|-------|----------------|----------------|-------|----|----------------|----------------------|--------------------------------------------------------|

| D/C#  | Hex    | <b>D</b> 7 | D6             | D5    | D4             | D3             | D2    | D1 | D0             | Command              | Description                                            |

| 0     | 81     | 1          | 0              | 0     | 0              | 0              | 0     | 0  | 1              | Set Contrast Control | Double byte command to select 1 out of 256             |

| 0     | A[7:0] | $A_7$      | A <sub>6</sub> | $A_5$ | A <sub>4</sub> | A <sub>3</sub> | $A_2$ | Aı | A <sub>0</sub> |                      | contrast steps. Contrast increases as the value        |

|       |        |            |                |       |                |                |       |    |                |                      | increases.                                             |

|       |        |            |                |       |                |                |       |    |                |                      | (RESET = 7Fh)                                          |

|       |        |            |                |       |                |                |       |    |                |                      |                                                        |

| 0     | A4/A5  | 1          | 0              | 1     | 0              | 0              | 1     | 0  | $X_0$          | Entire Display ON    | A4h, X <sub>0</sub> =0b: Resume to RAM content display |

|       |        |            |                |       |                |                |       |    |                |                      | (RESET)                                                |

|       |        |            |                |       |                |                |       |    |                |                      | Output follows RAM content                             |

|       |        |            |                |       |                |                |       |    |                |                      | A5h, X <sub>0</sub> =1b: Entire display ON             |

|       |        |            |                |       |                |                |       |    |                |                      | Output ignores RAM content                             |

| 0     | A6/A7  | 1          | 0              | 1     | 0              | 0              | 1     | 1  | $X_0$          | Set Normal/Inverse   | A6h, X[0]=0b: Normal display (RESET)                   |

|       |        |            |                |       |                |                |       |    |                | Display              | 0 in RAM: OFF in display panel                         |

|       |        |            |                |       |                |                |       |    |                |                      | 1 in RAM: ON in display panel                          |

|       |        |            |                |       |                |                |       |    |                |                      | A7h, X[0]=1b: Inverse display                          |

|       |        |            |                |       |                |                |       |    |                |                      | 0 in RAM: ON in display panel                          |

|       |        |            |                |       |                |                |       |    |                |                      | 1 in RAM: OFF in display panel                         |

| 0     | AE     | 1          | 0              | 1     | 0              | 1              | 1     | 1  | $X_0$          | Set Display ON/OFF   | AEh, X[0]=0b:Display OFF (sleep mode)                  |

|       | AF     |            |                |       |                |                |       |    | -              | . ,                  | (RESET)                                                |

|       |        |            |                |       |                |                |       |    |                |                      | AFh X[0]=1b:Display ON in normal mode                  |

|       |        |            |                |       |                |                |       |    |                |                      |                                                        |

| 2. :          | Scrolling | Com        | mano | l Tab | le |    |                |                |                |                   |                                                        |

|---------------|-----------|------------|------|-------|----|----|----------------|----------------|----------------|-------------------|--------------------------------------------------------|

| $\mathbf{D}/$ | C# Hex    | <b>D</b> 7 | D6   | D5    | D4 | D3 | D2             | D1             | D0             | Command           | Description                                            |

| 0             | 26/27     | 0          | 0    | 1     | 0  | 0  | 1              | 1              | $X_0$          | Continuous        | 26h, X[0]=0, Right Horizontal Scroll                   |

| 0             | A[7:0]    | 0          | 0    | 0     | 0  | 0  | 0              | 0              | 0              | Horizontal Scroll | 27h, X[0]=1, Left Horizontal Scroll                    |

| 0             | B[2:0]    | *          | *    | *     | *  | *  | $B_2$          | B <sub>1</sub> | B <sub>0</sub> | Setup             | (Horizontal scroll by 1 column)                        |

| 0             | C[2:0]    |            | *    | *     | *  | *  | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> |                   | A[7:0]: Dummy byte (Set as 00h)                        |

| 0             | D[2:0]    |            | *    | *     | *  | *  | D <sub>2</sub> | D <sub>1</sub> | $D_0$          |                   | B[2:0]: Define start page address                      |

| 0             | E[7:0]    |            | 0    | 0     | 0  | 0  | 0              | 0              | 0              |                   | 000b - PAGE0 011b - PAGE3   110b - PAGE6               |

| 0             | F[7:0]    |            | 1    | 1     | 1  | 1  | 1              | 1              | 1              |                   | 001b - PAGE1 100b - PAGE4 111b - PAGE7                 |

| ľ             | [,]       | 1          | 1    | ^     | 1  | -  | 1              | *              | 1              |                   | 010b - PAGE2 101b - PAGE5                              |

|               |           |            |      |       |    |    |                |                |                |                   | C[2:0] : Set time interval between each scroll step in |

|               |           |            |      |       |    |    |                |                |                |                   | terms of frame frequency                               |

|               |           |            |      |       |    |    |                |                |                |                   | 000b - 5 frames 100b - 3 frames                        |

|               |           |            |      |       |    |    |                |                |                |                   | 001b - 64 frames 101b - 4 frames                       |

|               |           |            |      |       |    |    |                |                |                |                   | 010b - 128 frames 110b - 25 frame                      |

|               |           |            |      |       |    |    |                |                |                |                   | 011b - 256 frames 111b - 2 frame                       |

|               |           |            |      |       |    |    |                |                |                |                   | D[2:0] : Define end page address                       |

|               |           |            |      |       |    |    |                |                |                |                   | 000b - PAGE0 011b - PAGE3 110b - PAGE6                 |

|               |           |            |      |       |    |    |                |                |                |                   | 001b - PAGE1 100b - PAGE4 111b - PAGE7                 |

|               |           |            |      |       |    |    |                |                |                |                   | 010b - PAGE2 101b - PAGE5                              |

|               |           |            |      |       |    |    |                |                |                |                   | The value of D[2:0] must be larger or equal            |

|               |           |            |      |       |    |    |                |                |                |                   | to B[2:0]                                              |

|               |           |            |      |       |    |    |                |                |                |                   | E[7:0]: Dummy byte (Set as 00h)                        |

|               |           |            |      |       |    |    |                |                |                |                   |                                                        |

|               |           |            |      |       |    |    |                |                |                |                   | F[7:0]: Dummy byte (Set as FFh)                        |

| $\mathbb{L}$  |           |            |      |       |    |    |                |                |                |                   |                                                        |

|                     | olling ( |                       |   |    |   |                                          |                                                                                     |                                                                                                   |                                       |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|----------|-----------------------|---|----|---|------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/C#                |          | D7                    |   | D5 | _ | D3                                       | D2                                                                                  | D1                                                                                                | D0                                    | Command                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D/C#<br>0<br>0<br>0 |          | 0<br>0<br>0<br>+<br>+ |   |    |   | D3<br>1<br>0<br>*<br>*<br>E <sub>3</sub> | 0<br>0<br>0<br>B <sub>2</sub><br>C <sub>2</sub><br>D <sub>2</sub><br>E <sub>2</sub> | D1<br>X <sub>1</sub><br>0<br>B <sub>1</sub><br>C <sub>1</sub><br>D <sub>1</sub><br>E <sub>1</sub> | X <sub>0</sub><br>0<br>B <sub>0</sub> | Continuous<br>Vertical and | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     |          |                       |   |    |   |                                          |                                                                                     |                                                                                                   |                                       |                            | Note  (i) No continuous vertical scrolling is available.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0                   | 2E       | 0                     | 0 | 1  | 0 | 1                                        | 1                                                                                   | 1                                                                                                 | 0                                     | Deactivate scroll          | Stop scrolling that is configured by command 26h/27h/29h/2Ah.  Note  1) After sending 2Eh command to descrive the scrolling action, the ram data needs to be rewritten.                                                                                                                                                                                                                                                                                                                                                                               |

| О                   | 2F       | 0                     | 0 | 1  | 0 | 1                                        | 1                                                                                   | 1                                                                                                 | 1                                     | Activate scroll            | Start scrolling that is configured by the scrolling setup commands: 26h/27h/29h/2Ah with the following valid sequences:  Valid command sequence 1: 26h; 2Fh. Valid command sequence 2: 27h; 2Fh. Valid command sequence 3: 29h; 2Fh. Valid command sequence 4: 2Ah; 2Fh. For example, if "26h; 2Ah; 2Fh." commands are issued, the setting in the last scrolling setup command, i.e. 2Ah in this case, will be executed. In other words, setting in the last scrolling setup command overwrites the setting in the previous scrolling setup commands. |

| 2   | . Scrollin           | Scrolling Command Table |   |                          |                                       |                                       |                                       |                                       |                                       |    |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|----------------------|-------------------------|---|--------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ļ   | /C# Hex              | D7                      | 7 | D6                       | D5                                    | D4                                    | D3                                    | D2                                    | D1                                    | D0 | Command | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 000 | A3<br>A[5::<br>B[6:: | )] [                    | 1 | 0<br>*<br>B <sub>6</sub> | 1<br>A <sub>5</sub><br>B <sub>5</sub> | 0<br>A <sub>4</sub><br>B <sub>4</sub> | 0<br>A <sub>3</sub><br>B <sub>3</sub> | 0<br>A <sub>2</sub><br>B <sub>2</sub> | 1<br>A <sub>1</sub><br>B <sub>1</sub> |    | Area    | A[5:0]: Set No. of rows in top fixed area. The No. of rows in top fixed area is referenced to the top of the GDDRAM (i.e. row 0).[RESET = 0]  B[6:0]: Set No. of rows in scroll area. This is the number of rows to be used for vertical scrolling. The scroll area starts in the first row below the top fixed area. [RESET = 64]  Note  A[5:0]+B[6:0] ← MUX ratio  A[5:0]+B[6:0] ← MUX ratio  A[6:0] ← MUX ratio  Set Display Start Line (X <sub>5</sub> X <sub>4</sub> X <sub>3</sub> X <sub>2</sub> X <sub>1</sub> X <sub>0</sub> of 40b∼7Fh) ← B[6:0]  The last row of the scroll area shifts to the first row of the scroll area.  For 64d MUX display  A[5:0] = 0, B[6:0] ← 64: whole area scrolls  A[5:0] = 0, B[6:0] < 64: central area scrolls  A[5:0] + B[6:0] < 64: bottom area scrolls  A[5:0] + B[6:0] < 64: bottom area scrolls |

| 3. A | ddressi                | ng Set | ting (                                | omm                                   | and T                                 | able                                  |                                       |                                       |                                       |                                                                   |                                                                                                                                                                                                                                        |

|------|------------------------|--------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/C# |                        |        |                                       |                                       |                                       |                                       |                                       | D1                                    | D0                                    | Command                                                           | Description                                                                                                                                                                                                                            |

| 0    | 00~0F                  | 0      | 0                                     | 0                                     | 0                                     | X <sub>3</sub>                        | X <sub>2</sub>                        | X <sub>1</sub>                        | X <sub>0</sub>                        | Set Lower Column<br>Start Address for<br>Page Addressing<br>Mode  | Set the lower nibble of the column start address register for Page Addressing Mode using X[3:0] as data bits. The initial display line register is reset to 0000b after RESET.  Note  1) This command is only for page addressing mode |

| О    | 10~1F                  | 0      | 0                                     | 0                                     | 1                                     | X <sub>3</sub>                        | $X_2$                                 | X <sub>1</sub>                        | X <sub>0</sub>                        | Set Higher Column<br>Start Address for<br>Page Addressing<br>Mode | Set the higher nibble of the column start address register for Page Addressing Mode using X[3:0] as data bits. The initial display line register is reset to 0000b after RESET.  Note  This command is only for page addressing mode   |

| -    | 20<br>A[1:0]           | 0 *    | 0 *                                   | 1 *                                   | 0 *                                   | 0                                     | 0                                     | 0<br>A <sub>1</sub>                   |                                       | Set Memory<br>Addressing Mode                                     | A[1:0] = 00b, Horizontal Addressing Mode<br>A[1:0] = 01b, Vertical Addressing Mode<br>A[1:0] = 10b, Page Addressing Mode (RESET)<br>A[1:0] = 11b, Invalid                                                                              |

| 0    | 21<br>A[6:0]<br>B[6:0] | 0 * *  | 0<br>A <sub>6</sub><br>B <sub>6</sub> | 1<br>A <sub>5</sub><br>B <sub>5</sub> | 0<br>A <sub>4</sub><br>B <sub>4</sub> | 0<br>A <sub>3</sub><br>B <sub>3</sub> | 0<br>A <sub>2</sub><br>B <sub>2</sub> | 0<br>A <sub>1</sub><br>B <sub>1</sub> | 1<br>A <sub>0</sub><br>B <sub>0</sub> | Set Column Address                                                | Setup column start and end address A[6:0]: Column start address, range: 0-127d, (RESET=0d)  B[6:0]: Column end address, range: 0-127d, (RESET =127d)  Note  This command is only for horizontal or vertical addressing mode.           |

| 3. A | ddressi | ng Set | ting ( | Comm | and 7 | [able |                |                |                |                                                       |                                                                                                                                             |

|------|---------|--------|--------|------|-------|-------|----------------|----------------|----------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| D/C# | Hex     | D7     | D6     | D5   | D4    | D3    | D2             | D1             | D0             | Command                                               | Description                                                                                                                                 |

| 0    | 22      | 0      | 0      | 1    | 0     | 0     | 0              | 1              | 0              | Set Page Address                                      | Setup page start and end address                                                                                                            |

| 0    | A[2:0]  | *      |        |      | *     |       | $A_2$          | $A_1$          | $A_0$          |                                                       | A[2:0] : Page start Address, range : 0-7d,                                                                                                  |

| 0    | B[2:0]  | *      |        |      | *     |       | $B_2$          | B <sub>1</sub> | B <sub>0</sub> |                                                       | (RESET = 0d)                                                                                                                                |

|      |         |        |        |      |       |       |                |                |                |                                                       | B[2:0]: Page end Address, range: 0-7d, (RESET = 7d)  Note  This command is only for horizontal or vertical addressing mode.                 |

| 0    | B0~B7   | 1      | 0      | 1    | 1     | 0     | X <sub>2</sub> | Xı             | "              | Set Page Start<br>Address for Page<br>Addressing Mode | Set GDDRAM Page Start Address  (PAGE0~PAGE7) for Page Addressing Mode using X[2:0].  Note  1) This command is only for page addressing mode |

*Version: 0* 10

| 4. Ha | rdware       | Conf | igura | tion (I             | Panel               | resolt              | tion                | & lay               | out rel             | lated) Command Tab                        | le                                                                                                                                                                                                              |

|-------|--------------|------|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D/C#  | Hex          | D7   | D6    | D5                  | D4                  | D3                  | D2                  | D1                  | D0                  | Command                                   | Description                                                                                                                                                                                                     |

| b     | 40~7F        | 0    | 1     | X,                  | X4                  | $X_3$               | X <sub>2</sub>      | Xı                  | $X_0$               | Set Display Start Line                    | Set display RAM display start line register from<br>0-63 using X <sub>2</sub> X <sub>3</sub> X <sub>2</sub> X <sub>3</sub> X <sub>0</sub> .<br>Display start line register is reset to 000000b<br>during RESET. |

| b     | A0/A1        | 1    | 0     | 1                   | 0                   | 0                   | 0                   | 0                   | $X_0$               | Set Segment Re-map                        | A0h, X[0]=0b: column address 0 is mapped to<br>SEG0 (RESET)<br>A1h, X[0]=1b: column address 127 is mapped to<br>SEG0                                                                                            |

| 0     | A8<br>A[5:0] | 1 *  | 0 *   | 1<br>A <sub>5</sub> | 0<br>A <sub>4</sub> | 1<br>A <sub>3</sub> | 0<br>A <sub>2</sub> | 0<br>A <sub>1</sub> | 0<br>A <sub>0</sub> | Set Multiplex Ratio                       | Set MUX ratio to N+1 MUX<br>N=A[5:0] : from 16MUX to 64MUX, RESET=<br>111111b (i.e. 63d, 64MUX)<br>A[5:0] from 0 to 14 are invalid entry.                                                                       |

| D     | C0/C8        | 1    | 1     | 0                   | 0                   | X <sub>3</sub>      | 0                   | 0                   | 0                   | Set COM Output<br>Scan Direction          | C0h, X[3]=0b: normal mode (RESET) Scan from<br>COM0 to COM[N-1]<br>C8h, X[3]=1b: remapped mode. Scan from<br>COM[N-1] to COM0<br>Where N is the Multiplex ratio.                                                |

| 0     | D3<br>A[5:0] | 1    | 1     | 0<br>A <sub>5</sub> | 1<br>A4             | 0<br>A <sub>3</sub> | 0<br>A <sub>2</sub> | 1<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | Set Display Offset                        | Set vertical shift by COM from 0d-63d<br>The value is reset to 00h after RESET.                                                                                                                                 |

| 0     | DA<br>A[5:4] | 1 0  | 0     | 0<br>A <sub>5</sub> | 1<br>A <sub>4</sub> | 0                   | 0                   | 1                   | 0                   | Set COM Pins<br>Hardware<br>Configuration | A[4]=0b, Sequential COM pin configuration A[4]=1b(RESET), Alternative COM pin configuration A[5]=0b(RESET), Disable COM Left/Right remap A[5]=1b, Enable COM Left/Right remap                                   |

| 5. Tit  | 5. Timing & Driving Scheme Setting Command Table |                     |                     |                     |                     |                     |                     |                     |                     |                                                              |                                                                                                                                                                                                                                                                                                                          |  |

|---------|--------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D/C#Hex |                                                  | D7                  | D6                  | D5                  | D4                  | D3                  | D2                  | D1                  | D0                  | Command                                                      | Description                                                                                                                                                                                                                                                                                                              |  |

|         | D5<br>A[7:0]                                     | 1<br>A <sub>7</sub> | 1<br>A <sub>6</sub> | 0<br>A <sub>5</sub> | 1<br>A <sub>4</sub> | 0<br>A <sub>3</sub> | 1<br>A <sub>2</sub> | 0<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | Set Display Clock<br>Divide<br>Ratio/Oscillator<br>Frequency | A[3:0]: Define the divide ratio (D) of the display clocks (DCLK): Divide ratio= A[3:0] + 1, RESET is 0000b (divide ratio = 1)  A[7:4]: Set the Oscillator Frequency, Fosc. Oscillator Frequency increases with the value of A[7:4] and vice versa. RESET is 1000b Range:0000b~1111b Frequency increases as setting value |  |

| [       | D9<br>A[7:0]                                     | 1<br>A <sub>7</sub> | 1<br>A <sub>6</sub> | 0<br>A <sub>5</sub> | 1<br>A4             | 1<br>A <sub>3</sub> | 0<br>A <sub>2</sub> | 0<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | Set Pre-charge Period                                        | increases.  A[3:0]: Phase 1 period of up to 15 DCLK clocks 0 is invalid entry (RESET=2h)  A[7:4]: Phase 2 period of up to 15 DCLK clocks 0 is invalid entry (RESET=2h)                                                                                                                                                   |  |

| ľ       | DB<br>A[6:4]                                     | 0                   | 1<br>A <sub>6</sub> | 0<br>A <sub>5</sub> | 1<br>A4             | 0                   | 0                   | 0                   | 0                   | Set V <sub>COMH</sub> Deselect<br>Level                      | A[6:4] Hex Code  000b 00h ~ 0.65 x Vcc  010b 20h ~ 0.77 x Vcc (RESET)  011b 30h ~ 0.83 x Vcc                                                                                                                                                                                                                             |  |

| 0       | E3                                               | 1                   | 1                   | 1                   | 0                   | 0                   | 0                   | 1                   | 1                   | NOP                                                          | Command for no operation                                                                                                                                                                                                                                                                                                 |  |

Note

(1) "a" stands for "Don't care".

### 9. FUNCTIONAL SPECIFICATION

### 9.1 Commands

Refer to the Technical Manual for the SSD1306B

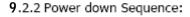

### 9.2 Power down and Power up Sequence

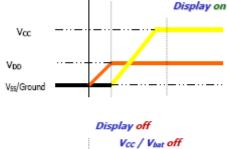

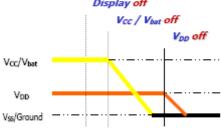

To protect OEL panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. It gives the OEL panel enough time to complete the action of charge and discharge before/after the operation.

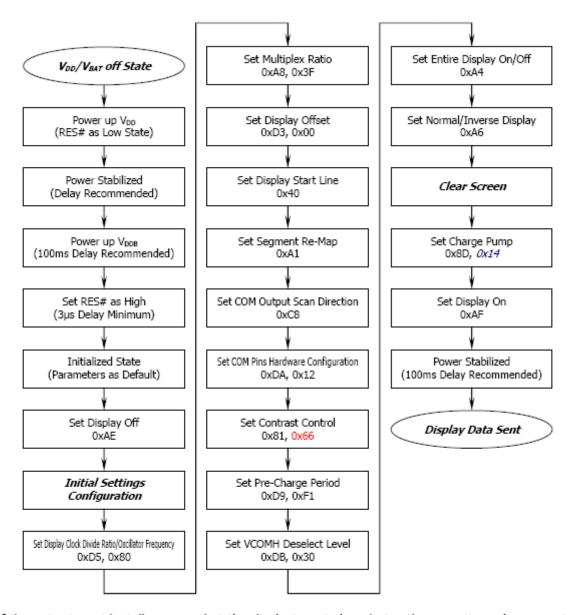

### 9.2.1 Power up Sequence:

- 1. Power up V<sub>DD</sub>

- 2. Send Display off command

- 3. Initialization

- 4. Clear Screen

- 5. Power up V<sub>CC</sub>/ V<sub>BAT</sub>

- Delay 100ms (When V<sub>CC</sub> is stable)

- 7. Send Display on command

- 1. Send Display off command

- Power down V<sub>CC</sub> / V<sub>BAT</sub>

- Delay 100ms (When V<sub>CC</sub> / V<sub>BAT</sub> is reach 0 and panel is completely discharges)

- 4. Power down VDD

$V_{DD} / V_{BAT}$  on  $V_{CC}$  on

### Note 13:

- Since an ESD protection circuit is connected between V<sub>DD</sub> and V<sub>CC</sub> inside the driver IC, V<sub>CC</sub> becomes lower than V<sub>DD</sub> whenever V<sub>DD</sub> is ON and V<sub>CC</sub> is OFF.

- V<sub>CC</sub> / V<sub>BAT</sub> should be kept float (disable) when it is OFF.

- Power Pins (V<sub>DD</sub>, V<sub>CC</sub>, V<sub>BAT</sub>) can never be pulled to ground under any circumstance.

- 4) VDD should not be power down before VCC / VBAT power down.

### 9.3 Reset Circuit

When RES# input is low, the chip is initialized with the following status:

- 1. Display is OFF

- 2. 128×64 Display Mode

- Normal segment and display data column and row address mapping (SEG0 mapped to column address 00h and COM0 mapped to row address 00h)

- 4. Shift register data clear in serial interface

- 5. Display start line is set at display RAM address 0

- 6. Column address counter is set at 0

- 7. Normal scan direction of the COM outputs

- 8. Contrast control register is set at 7Fh

- 9. Normal display mode (Equivalent to A4h command)

### 9.4 Actual Application Example

If the noise is accidentally occurred at the displaying window during the operation, please reset the display in order to recover the display function.

*Version: 0* 13

### <Power down Sequence> Power Stabilized Normal Operation VDD/VBAT off State (100ms Delay Recommended) Power down V<sub>BAT</sub> Set Display Off (50ms Delay Recommended) 0xAE Set Charge Pump Power down V<sub>DD</sub> 0x8D, 0x10 <Entering Sleep Mode> Set Charge Pump Normal Operation Sleep Mode 0x8D, 0x10 Set Display Off Power down V<sub>BAT</sub> 0xAE <Exiting Sleep Mode> Set Charge Pump Power Stabilized Sleep Mode 0x8D, 0x14 (100ms Delay Recommended) Set Display On Power up V<sub>BAT</sub> Normal Operation 0xAF (100ms Delay Recommended)

### 10. MODULE ACCEPT QUALITY LEVEL (AQL)

10.1 AQL Standard Value: Critical Defect =0.1, Major Defect=0.65; Minor Defect =2.5.

10.2 Inspection Standard: MIL-STD-105E Table Normal Inspection Single Sampling Level II

### 11. RELIABILITY TEST.

### 11.1 Contents of Reliability Tests

| Item                                | Conditions                               | Criteria        |  |

|-------------------------------------|------------------------------------------|-----------------|--|

| High Temperature Operation          | 70°C, 240 hrs                            |                 |  |

| Low Temperature Operation           | -40°C, 240 hrs                           | The operational |  |

| High Temperature Storage            | 85°C, 240 hrs                            |                 |  |

| Low Temperature Storage             | -40°C, 240 hrs                           | functions work. |  |

| High Temperature/Humidity Operation | 60°C, 90% RH, 120 hrs                    |                 |  |

| Thermal Shock                       | -40°C ⇔ 85°C, 24 cycles<br>60 mins dwell |                 |  |

<sup>\*</sup> The samples used for the above tests do not include polarizer.

### 11.2 Failure Check Standard

After the completion of the described reliability test, the samples were left at room temperature for 2 hrs prior to conducting the failure test at  $23\pm5^{\circ}$ C;  $55\pm15^{\circ}$  RH.

### 12. QUALITY DESCRIPTION & APPLICTION NOTE

Please refer to "General Inspection Criteria" document.

*Version: 0* 15

<sup>\*</sup> No moisture condensation is observed during tests.