# nRF52810

## **Product Specification** v1.0

4430\_161 v1.0 / 2017-09-29

# Key features

#### Key features:

#### • 2.4 GHz transceiver

- -96 dBm sensitivity in *Bluetooth*<sup>®</sup> low energy mode

- Supported data rates: 1 Mbps, 2 Mbps  $\textit{Bluetooth}^{\text{$^{\circ}$}}$  low energy mode

- -20 to +4 dBm TX power, configurable in 4 dB steps

- On-chip balun (single-ended RF)

- 4.6 mA peak current in TX (0 dBm)

- 4.6 mA peak current in RX

- RSSI (1 dB resolution)

- ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit processor, 64 MHz

- 144 EEMBC CoreMark<sup>®</sup> score running from flash memory

- 34.4 µA/MHz running from flash memory

- 32.8 μA/MHz running from RAM

- Serial wire debug (SWD)

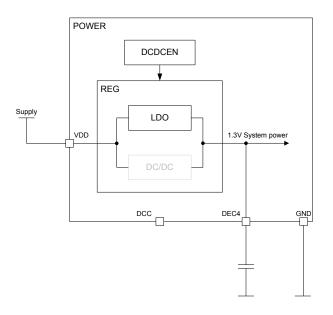

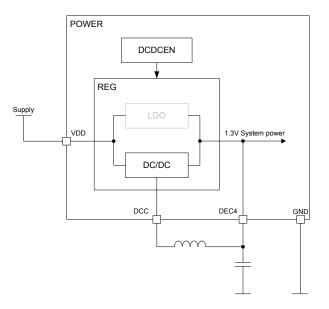

- Flexible power management

- 1.7 V-3.6 V supply voltage range

- Fully automatic LDO and DC/DC regulator system

- Fast wake-up using 64 MHz internal oscillator

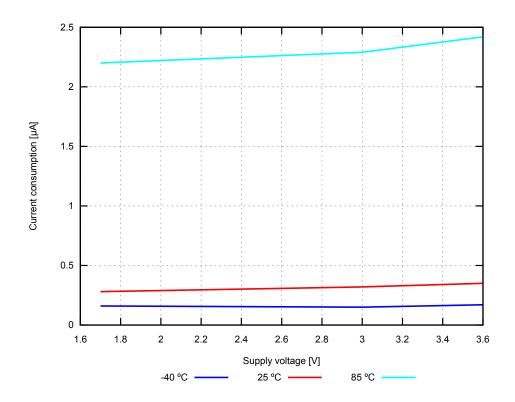

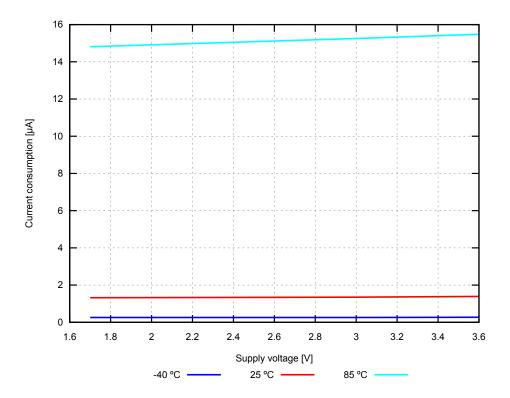

- 0.3 µA at 3 V in System OFF mode, no RAM retention

- 0.5 μA at 3 V in System OFF mode with full 24 kB RAM retention

- 1.5  $\mu$ A at 3 V in System ON mode, with full 24 kB RAM retention, wake on RTC

- 192 kB flash and 24 kB RAM

- Nordic SoftDevice ready

•

- Support for concurrent multi-protocol

- 12-bit, 200 ksps ADC 8 configurable channels with programmable gain

- 64 level comparator

- Temperature sensor

- Up to 32 general purpose I/O pins

- 4-channel pulse width modulator (PWM) unit with EasyDMA

- Digital microphone interface (PDM)

- 3x 32-bit timer with counter mode

- SPI master/slave with EasyDMA

- I2C compatible 2-wire master/slave

- UART (CTS/RTS) with EasyDMA

- Programmable peripheral interconnect (PPI)

- Quadrature decoder (QDEC)

- AES HW encryption with EasyDMA

- 2x real-time counter (RTC)

- Single crystal operation

- Package variants

- QFN48 package, 6 x 6 mm

- QFN32 package, 5 x 5 mm

#### Applications:

- Computer peripherals and I/O devices

- Mouse

- Keyboard

- Mobile HID

- CE remote controls

- Network processor

- Wearables

- Virtual reality headsets

- Health and medical

- Enterprise lighting

- Industrial

- Commercial

- Retail

- Beacons

- Connectivity device in multi-chip solutions

# Contents

|   | Key features.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ii                                                                                                                                      |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Revision history                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                                                                                       |

| 2 | 2.1 Document naming and status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10<br>10<br>11<br>11<br>11<br>11                                                                                                        |

| 3 | Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                                                                                                      |

| 4 | <ul> <li>4.1 CPU</li> <li>4.1.1 Electrical specification</li> <li>4.2 CPU and support module configuration</li> <li>4.2 Memory</li> <li>4.2.1 RAM - Random access memory</li> <li>4.2.2 Flash - Non-volatile memory</li> <li>4.2.3 Memory map</li> <li>4.2.4 Instantiation</li> <li>4.3 NVMC — Non-volatile memory controller</li> <li>4.3.1 Writing to flash</li> <li>4.3.2 Erasing a page in flash</li> <li>4.3.3 Writing to user information configuration registers (UICR)</li> <li>4.3.4 Erasing user information configuration registers (UICR)</li> <li>4.3.5 Erase all</li> <li>4.3.6 Registers</li> <li>4.3.7 Electrical specification</li> <li>4.5 UICR — User information configuration registers</li> <li>4.5 UICR — User information configuration registers</li> <li>4.5.1 Registers</li> <li>4.5 LICR — Dese information configuration registers</li> <li>4.5.1 Registers</li> <li>4.5 LICR — Dese information configuration registers</li> <li>4.5.1 Registers</li> <li>4.5 LICR — Control Access Port</li> <li>4.8.2 CTRL-AP - Control Access Port</li> <li>4.8.3 Debug interface mode</li> </ul> | <b>L4</b><br>14<br>14<br>15<br>16<br>16<br>16<br>17<br>18<br>18<br>19<br>19<br>21<br>22<br>22<br>32<br>49<br>50<br>51<br>51<br>53<br>54 |

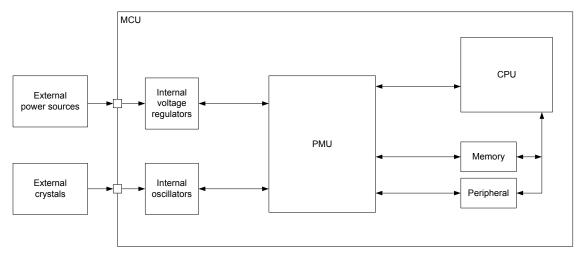

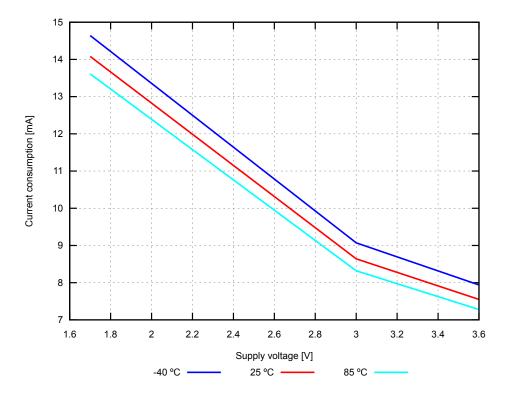

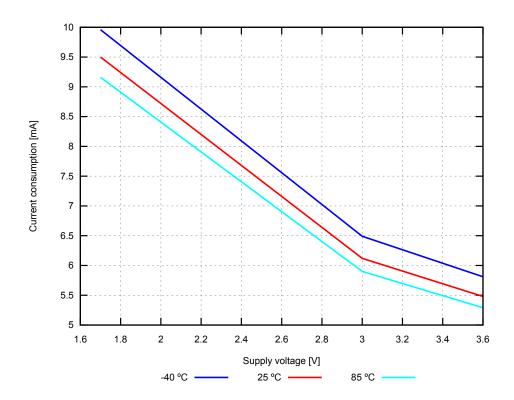

| 5 | 5.1 Power management unit (PMU)      5.2 Current consumption      5.2.1 Electrical specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55<br>55<br>55<br>56<br>61                                                                                                              |

|    | 7.3 Reference circuitry                               | 468   |

|----|-------------------------------------------------------|-------|

|    | 7.3.1 Schematic QFAA QFN48 with internal LDO setup    | . 468 |

|    | 7.3.2 Schematic QFAA QFN48 with DC/DC regulator setup | 470   |

|    | 7.3.3 Schematic QCAA QFN32 with internal LDO setup    | . 471 |

|    | 7.3.4 Schematic QCAA QFN32 with DC/DC regulator setup | 472   |

|    | 7.3.5 PCB guidelines                                  | 473   |

|    | 7.3.6 PCB layout example                              | . 474 |

|    |                                                       |       |

| 8  | Recommended operating conditions                      | 476   |

|    |                                                       |       |

| 9  | Absolute maximum ratings                              | 477   |

|    |                                                       |       |

| 10 | Ordering information                                  | 478   |

|    | 10.1 IC marking                                       | 478   |

|    | 10.2 Box labels                                       |       |

|    | 10.3 Order code                                       | 479   |

|    | 10.4 Code ranges and values                           | 480   |

|    | 10.5 Product options                                  | 481   |

|    |                                                       |       |

| 11 | Liability disclaimer                                  | 483   |

Downloaded from Arrow.com.

# 1 Revision history

| Date           | Version | Description   |

|----------------|---------|---------------|

| September 2017 | 1.0     | First release |

4430\_161 v1.0

# 2 About this document

This product specification is organized into chapters based on the modules and peripherals that are available in this IC.

The peripheral descriptions are divided into separate sections that include the following information:

- A detailed functional description of the peripheral

- Register configuration for the peripheral

- Electrical specification tables, containing performance data which apply for the operating conditions described in Recommended operating conditions on page 476.

## 2.1 Document naming and status

Nordic uses three distinct names for this document, which are reflecting the maturity and the status of the document and its content.

| Document name                           | Description                                                                                                                                                                                                                                                                           |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective Product Specification (OPS)   | Applies to document versions up to 0.7.<br>This product specification contains target<br>specifications for product development.                                                                                                                                                      |

| Preliminary Product Specification (PPS) | Applies to document versions 0.7 and up to 1.0.<br>This product specification contains preliminary<br>data. Supplementary data may be published from<br>Nordic Semiconductor ASA later.                                                                                               |

| Product Specification (PS)              | Applies to document versions 1.0 and higher.<br>This product specification contains final product<br>specifications. Nordic Semiconductor ASA reserves<br>the right to make changes at any time without<br>notice in order to improve design and supply the<br>best possible product. |

Table 1: Defined document names

## 2.2 Peripheral naming and abbreviations

Every peripheral has a unique capitalized name or an abbreviation of its name, e.g. TIMER, used for identification and reference. This name is used in chapter headings and references, and it will appear in the ARM<sup>®</sup> Cortex<sup>®</sup> Microcontroller Software Interface Standard (CMSIS) hardware abstraction layer to identify the peripheral.

The peripheral instance name, which is different from the peripheral name, is constructed using the peripheral name followed by a numbered postfix, starting with 0, for example, TIMERO. A postfix is normally only used if a peripheral can be instantiated more than once. The peripheral instance name is also used in the CMSIS to identify the peripheral instance.

# 2.3 Register tables

Individual registers are described using register tables. These tables are built up of two sections. The first three colored rows describe the position and size of the different fields in the register. The following rows describe the fields in more detail.

## 2.3.1 Fields and values

The **Id (Field Id)** row specifies the bits that belong to the different fields in the register. If a field has enumerated values, then every value will be identified with a unique value id in the **Value Id** column.

A blank space means that the field is reserved and read as undefined, and it also must be written as 0 to secure forward compatibility. If a register is divided into more than one field, a unique field name is specified for each field in the **Field** column. The **Value Id** may be omitted in the single-bit bit fields when values can be substituted with a Boolean type enumerator range, e.g. true/false, disable(d)/enable(d), on/ off, and so on.

Values are usually provided as decimal or hexadecimal. Hexadecimal values have a  $0 \times$  prefix, decimal values have no prefix.

The Value column can be populated in the following ways:

- Individual enumerated values, for example 1, 3, 9.

- Range of values, e.g. [0..4], indicating all values from and including 0 and 4.

- Implicit values. If no values are indicated in the **Value** column, all bit combinations are supported, or alternatively the field's translation and limitations are described in the text instead.

If two or more fields are closely related, the **Value Id**, **Value**, and **Description** may be omitted for all but the first field. Subsequent fields will indicate inheritance with '..'.

A feature marked **Deprecated** should not be used for new designs.

# 2.4 Registers

| Register | Offset | Description                                       |

|----------|--------|---------------------------------------------------|

| DUMMY    | 0x514  | Example of a register controlling a dummy feature |

|          |        |                                                   |

Table 2: Register Overview

## 2.4.1 DUMMY

Address offset: 0x514

Example of a register controlling a dummy feature

| Bit number       |              | 31 30 29 28 27 2 | 26 25 24 23 22 21 2 | 20 19 18 17 16 15 14   | 13 12 11 10 9    | 87654 | 3210 |

|------------------|--------------|------------------|---------------------|------------------------|------------------|-------|------|

| Id               |              | D                | DDD                 | ссс                    |                  | В     | A A  |

| Reset 0x00050002 |              | 0 0 0 0 0        | 0 0 0 0 0 0         | 0 0 1 0 1 0 0          | 0 0 0 0 0        | 00000 | 0010 |

| Id RW Field      |              |                  |                     |                        |                  |       |      |

| A RW FIELD_A     |              |                  | Example of          | of a field with severa | l enumerated va  | alues |      |

|                  | Disabled     | 0                | The exam            | ple feature is disable | ed               |       |      |

|                  | NormalMode   | 1                | The exam            | ple feature is enable  | d in normal mo   | de    |      |

|                  | ExtendedMode | 2                | The exam            | ple feature is enable  | ed along with ex | tra   |      |

|                  |              |                  | functiona           | lity                   |                  |       |      |

| Bit number       |            | 31 30 29 28 | 8 27 2 | 6 25 | 24 2 | 23 22 | 2 2 1 | 20   | 19    | 18   | 17   | 16   | 15   | 14 1  | 3 12  | 2 1 1 | . 10 | 9   | 8   | 7 | 6 | 5 4 | 43  | 2    | 1 0    |

|------------------|------------|-------------|--------|------|------|-------|-------|------|-------|------|------|------|------|-------|-------|-------|------|-----|-----|---|---|-----|-----|------|--------|

| Id               |            |             | DD     | D    | D    |       |       |      |       | С    | С    | С    |      |       |       |       |      |     | В   |   |   |     |     |      | A A    |

| Reset 0x00050002 |            | 0 0 0 0     | 00     | 0 0  | 0    | 0 0   | 0     | 0    | 0     | 1    | 0    | 1    | 0    | 0     | 0 0   | 0     | 0    | 0   | 0   | 0 | 0 | 0 ( | 0 0 | 0    | 1 0    |

|                  |            |             |        |      |      |       |       |      |       |      |      |      |      |       |       |       |      |     |     |   |   |     |     |      |        |

| B RW FIELD_B     |            |             |        |      | I    | Exan  | nple  | ofa  | a de  | epro | eca  | ted  | fie  | ld    |       |       |      |     |     |   |   |     | D   | epro | ecated |

|                  | Disabled   | 0           |        |      | -    | The o | over  | ride | e fea | atu  | re i | s d  | isak | led   |       |       |      |     |     |   |   |     |     |      |        |

|                  | Enabled    | 1           |        |      | -    | The o | over  | ride | e fei | atu  | re i | s e  | nab  | led   |       |       |      |     |     |   |   |     |     |      |        |

| C RW FIELD_C     |            |             |        |      | I    | Exan  | nple  | of a | a fie | eld  | wit  | h a  | val  | id ra | ange  | e of  | valı | ues |     |   |   |     |     |      |        |

|                  | ValidRange | [27]        |        |      | I    | Exan  | nple  | ofa  | allo  | we   | d va | alue | es f | or tl | nis f | ield  |      |     |     |   |   |     |     |      |        |

| D RW FIELD D     |            |             |        |      |      | Exan  | مامد  | of   | , fic | hld  | i+   | h n  | o re | octri | ctio  | n 0   | n +h |     | Jur |   |   |     |     |      |        |

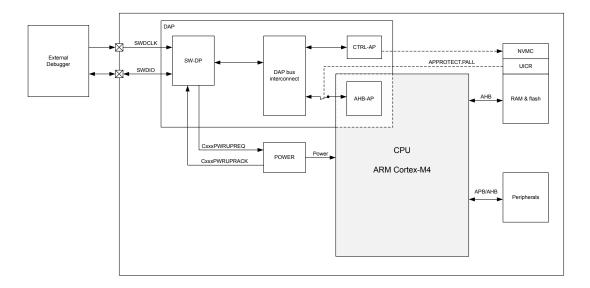

# **3** Block diagram

This block diagram illustrates the overall system. Arrows with white heads indicate signals that share physical pins with other signals.

Figure 1: Block diagram

# 4 Core components

# 4.1 CPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processor has a 32-bit instruction set (Thumb<sup>®</sup>-2 technology) that implements a superset of 16 and 32-bit instructions to maximize code density and performance.

This processor implements several features that enable energy-efficient arithmetic and high-performance signal processing including:

- Digital signal processing (DSP) instructions

- Single-cycle multiply and accumulate (MAC) instructions

- Hardware divide

- 8 and 16-bit single instruction multiple data (SIMD) instructions

The ARM Cortex Microcontroller Software Interface Standard (CMSIS) hardware abstraction layer for the ARM Cortex processor series is implemented and available for the M4 CPU.

Real-time execution is highly deterministic in thread mode, to and from sleep modes, and when handling events at configurable priority levels via the nested vectored interrupt controller (NVIC).

Executing code from flash will have a wait state penalty on the nRF52 Series. The section Electrical specification on page 14 shows CPU performance parameters including wait states in different modes, CPU current and efficiency, and processing power and efficiency based on the CoreMark<sup>®</sup> benchmark.

The ARM System Timer (SysTick) is present on the device. The SysTick's clock will only tick when the CPU is running or when the system is in debug interface mode.

## 4.1.1 Electrical specification

#### 4.1.1.1 CPU performance

The CPU clock speed is 64 MHz. Current and efficiency data is taken when in System ON and the CPU is executing the CoreMark<sup>®</sup> benchmark. It includes power regulator and clock base currents. All other blocks are IDLE.

| Symbol                  | Description                                  | Min. | Тур. | Max. | Units     |

|-------------------------|----------------------------------------------|------|------|------|-----------|

| W <sub>FLASH</sub>      | CPU wait states, running from flash          | 0    |      | 2    |           |

| W <sub>RAM</sub>        | CPU wait states, running from RAM            |      |      | 0    |           |

| CM <sub>FLASH</sub>     | CoreMark <sup>1</sup> , running from flash   |      | 144  |      | CoreMark  |

| CM <sub>FLASH/MHz</sub> | CoreMark per MHz, running from flash         |      | 2.25 |      | Corel     |

|                         |                                              |      |      |      | MHz       |

| CM <sub>FLASH/mA</sub>  | CoreMark per mA, running from flash, DCDC 3V |      | 60   |      | CoreMark/ |

|                         |                                              |      |      |      | mA        |

## 4.1.2 CPU and support module configuration

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processor has a number of CPU options and support modules implemented on the device.

<sup>&</sup>lt;sup>1</sup> Using IAR v6.50.1.4452 with flags --endian=little --cpu=Cortex-M4 -e --fpu=VFPv4\_sp –Ohs -no\_size\_constraints

|                 | <u> </u>                              |               |

|-----------------|---------------------------------------|---------------|

| Option / Module | Description                           | Implemented   |

| Core options    |                                       |               |

| NVIC            | Nested vector interrupt controller    | 30 vectors    |

| PRIORITIES      | Priority bits                         | 3             |

| WIC             | Wakeup interrupt controller           | NO            |

| Endianness      | Memory system endianness              | Little endian |

| Bit-banding     | Bit banded memory                     | NO            |

| DWT             | Data watchpoint and trace             | NO            |

| SysTick         | System tick timer                     | YES           |

| Modules         |                                       |               |

| MPU             | Memory protection unit                | YES           |

| FPU             | Floating-point unit                   | NO            |

| DAP             | Debug access port                     | YES           |

| ETM             | Embedded trace macrocell              | NO            |

| ITM             | Instrumentation trace macrocell       | NO            |

| TPIU            | Trace port interface unit             | NO            |

| ETB             | Embedded trace buffer                 | NO            |

| FPB             | Flash patch and breakpoint unit       | YES           |

| HTM             | AMBA <sup>®</sup> AHB trace macrocell | NO            |

|                 |                                       |               |

## 4.2 Memory

The nRF52810 contains flash and RAM that can be used for code and data storage.

The amount of RAM and flash will vary depending on variant, see Memory variants on page 15.

| Device name   | RAM   | Flash  | Comments |

|---------------|-------|--------|----------|

| nRF52810-QFAA | 24 kB | 192 kB |          |

#### Table 3: Memory variants

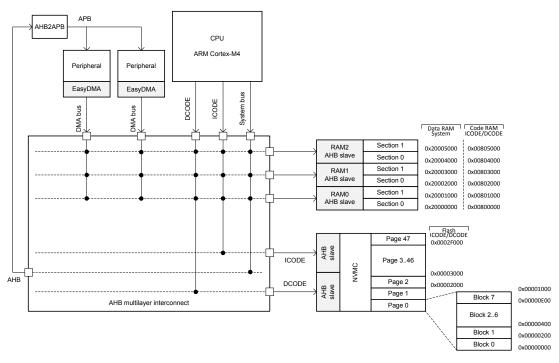

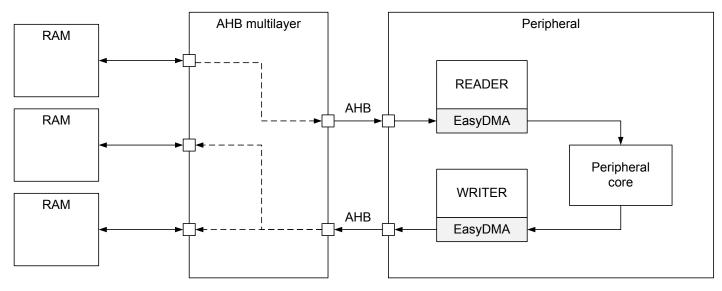

The CPU and the EasyDMA can access memory via the AHB multilayer interconnect. The CPU is also able to access peripherals via the AHB multilayer interconnect, as illustrated in Memory layout on page 16.

Figure 2: Memory layout

See AHB multilayer on page 50 and EasyDMA on page 48 for more information about the AHB multilayer interconnect and the EasyDMA.

The same physical RAM is mapped to both the Data RAM region and the Code RAM region. It is up to the application to partition the RAM within these regions so that one does not corrupt the other.

#### 4.2.1 RAM - Random access memory

The RAM interface is divided into multiple RAM AHB slaves.

Each RAM AHB slave is connected to two 4-kilobyte RAM sections, see Section 0 and Section 1 in Memory layout on page 16.

Each of the RAM sections have separate power control for System ON and System OFF mode operation, which is configured via RAM register (see the POWER — Power supply on page 61).

## 4.2.2 Flash - Non-volatile memory

The flash can be read an unlimited number of times by the CPU, but it has restrictions on the number of times it can be written and erased, and also on how it can be written.

Writing to flash is managed by the non-volatile memory controller (NVMC), see NVMC — Non-volatile memory controller on page 18.

The flash is divided into multiple 4 kB pages that can be accessed by the CPU via both the ICODE and DCODE buses as shown in, Memory layout on page 16. Each page is divided into 8 blocks.

#### 4.2.3 Memory map

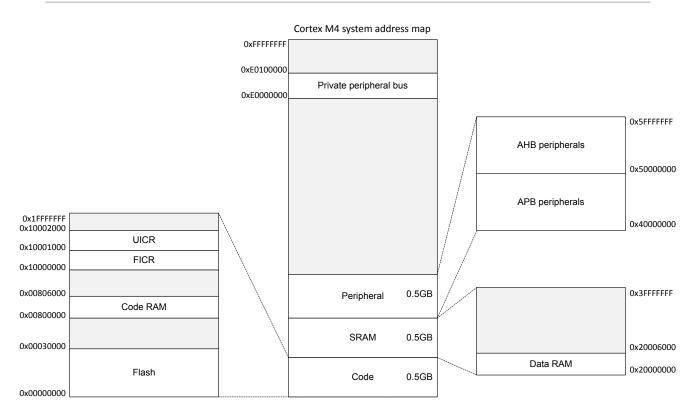

The complete memory map is shown in Memory map on page 17. As described in Memory on page 15, Code RAM and Data RAM are the same physical RAM.

#### Figure 3: Memory map

#### 4.2.4 Instantiation

| ID | Base Address | Peripheral | Instance | Description                                              |

|----|--------------|------------|----------|----------------------------------------------------------|

| 0  | 0x40000000   | CLOCK      | CLOCK    | Clock control                                            |

| 0  | 0x40000000   | BPROT      | BPROT    | Block protect                                            |

| 0  | 0x40000000   | POWER      | POWER    | Power control                                            |

| 1  | 0x40001000   | RADIO      | RADIO    | 2.4 GHz radio                                            |

| 2  | 0x40002000   | UARTE      | UARTEO   | Universal asynchronous receiver/transmitter with EasyDMA |

| 3  | 0x40003000   | TWIM       | TWIM0    | Two-wire interface master                                |

| 3  | 0x40003000   | TWIS       | TWIS0    | Two-wire interface slave                                 |

| 4  | 0x40004000   | SPIS       | SPIS0    | SPI slave                                                |

| 4  | 0x40004000   | SPIM       | SPIMO    | SPI master                                               |

| 6  | 0x40006000   | GPIOTE     | GPIOTE   | GPIO tasks and events                                    |

| 7  | 0x40007000   | SAADC      | SAADC    | Analog-to-digital converter                              |

| 8  | 0x40008000   | TIMER      | TIMER0   | Timer 0                                                  |

| 9  | 0x40009000   | TIMER      | TIMER1   | Timer 1                                                  |

| 10 | 0x4000A000   | TIMER      | TIMER2   | Timer 2                                                  |

| 11 | 0x4000B000   | RTC        | RTC0     | Real-time counter 0                                      |

| 12 | 0x4000C000   | TEMP       | TEMP     | Temperature sensor                                       |

| 13 | 0x4000D000   | RNG        | RNG      | Random number generator                                  |

| 14 | 0x4000E000   | ECB        | ECB      | AES Electronic Codebook (ECB) mode block encryption      |

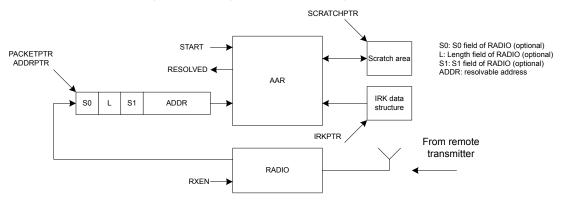

| 15 | 0x4000F000   | AAR        | AAR      | Accelerated address resolver                             |

| 15 | 0x4000F000   | ССМ        | ССМ      | AES CCM mode encryption                                  |

| 16 | 0x40010000   | WDT        | WDT      | Watchdog timer                                           |

| 17 | 0x40011000   | RTC        | RTC1     | Real-time counter 1                                      |

| 18 | 0x40012000   | QDEC       | QDEC     | Quadrature decoder                                       |

| 19 | 0x40013000   | COMP       | COMP     | General purpose comparator                               |

| 20 | 0x40014000   | SWI        | SWI0     | Software interrupt 0                                     |

| 20 | 0x40014000   | EGU        | EGU0     | Event generator unit 0                                   |

|    |              |            |          |                                                          |

Downloaded from Arrow.com.

| 10  | Dava Adduses | Deviational | luster as | Description                                             |

|-----|--------------|-------------|-----------|---------------------------------------------------------|

| ID  | Base Address | Peripheral  | Instance  | Description                                             |

| 21  | 0x40015000   | EGU         | EGU1      | Event generator unit 1                                  |

| 21  | 0x40015000   | SWI         | SWI1      | Software interrupt 1                                    |

| 22  | 0x40016000   | SWI         | SWI2      | Software interrupt 2                                    |

| 23  | 0x40017000   | SWI         | SWI3      | Software interrupt 3                                    |

| 24  | 0x40018000   | SWI         | SWI4      | Software interrupt 4                                    |

| 25  | 0x40019000   | SWI         | SWI5      | Software interrupt 5                                    |

| 28  | 0x4001C000   | PWM         | PWM0      | Pulse-width modulation unit 0                           |

| 29  | 0x4001D000   | PDM         | PDM       | Pulse-density modulation (digital microphone interface) |

| 30  | 0x4001E000   | NVMC        | NVMC      | Non-volatile memory controller                          |

| 31  | 0x4001F000   | PPI         | PPI       | Programmable peripheral interconnect                    |

| 0   | 0x5000000    | GPIO        | P0        | General purpose input and output                        |

| N/A | 0x1000000    | FICR        | FICR      | Factory information configuration                       |

| N/A | 0x10001000   | UICR        | UICR      | User information configuration                          |

Table 4: Instantiation table

# 4.3 NVMC — Non-volatile memory controller

The non-volatile memory controller (NVMC) is used for writing and erasing of the internal flash memory and the UICR (user information configuration registers).

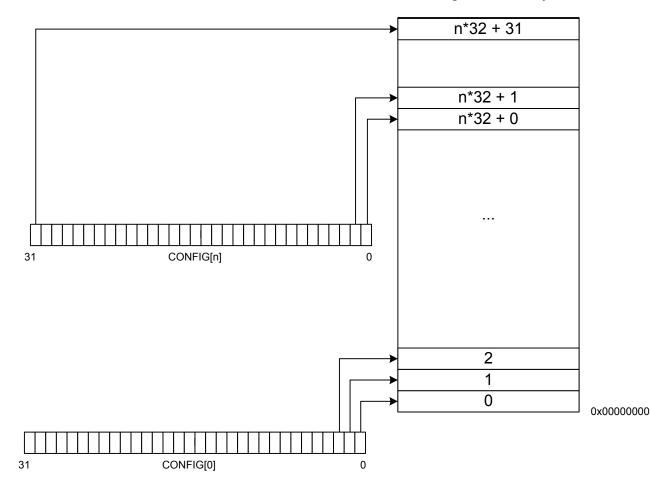

The CONFIG register is used to enable the NVMC for writing (CONFIG.WEN) and erasing (CONFIG.EEN), see CONFIG on page 19. The user must make sure that writing and erasing are not enabled at the same time. Having both enabled at the same time may result in unpredictable behavior.

#### 4.3.1 Writing to flash

When writing is enabled, full 32-bit words are written to word-aligned addresses in flash.

As illustrated in Memory on page 15, the flash is divided into multiple pages that in turn are divided into multiple blocks. The same block in flash can only be written  $n_{WRITE}$  number of times before an erase must be performed using ERASEPAGE or ERASEALL. See the memory size and organization in Memory on page 15 for block size.

The NVMC is only able to write 0 to bits in the flash that are erased (set to 1). It cannot rewrite a bit back to 1. Only full 32-bit words can be written to flash using the NVMC interface. To write less than 32 bits, write the data as a full 32-bit word and set all the bits that should remain unchanged in the word to 1. Note that the restriction on the number of writes ( $n_{WRITE}$ ) still applies in this case.

Only word-aligned writes are allowed. Byte or half-word-aligned writes will result in a hard fault.

The time it takes to write a word to flash is specified by  $t_{WRITE}$ . The CPU is halted if the CPU executes code from the flash while the NVMC is writing to the flash.

## 4.3.2 Erasing a page in flash

When erase is enabled, the flash memory can be erased page by page using the ERASEPAGE register.

After erasing a flash page, all bits in the page are set to 1. The time it takes to erase a page is specified by  $t_{ERASEPAGE}$ . The CPU is halted if the CPU executes code from the flash while the NVMC is writing to the flash.

## 4.3.3 Writing to user information configuration registers (UICR)

User information configuration registers (UICR) are written in the same way as flash. After UICR has been written, the new UICR configuration will take effect after a reset.

UICR can only be written n<sub>WRITE</sub> number of times before an erase must be performed using ERASEUICR or ERASEALL. The time it takes to write a word to UICR is specified by t<sub>WRITE</sub>. The CPU is halted if the CPU executes code from the flash while the NVMC is writing to the UICR.

#### 4.3.4 Erasing user information configuration registers (UICR)

When erase is enabled, UICR can be erased using the ERASEUICR register.

After erasing UICR all bits in UICR are set to 1. The time it takes to erase UICR is specified by t<sub>ERASEPAGE</sub>. The CPU is halted if the CPU executes code from the flash while the NVMC performs the erase operation.

#### 4.3.5 Erase all

When erase is enabled, flash and UICR can be erased completely in one operation by using the ERASEALL register. ERASEALL will not erase the factory information configuration registers (FICR).

The time it takes to perform an ERASEALL command is specified by t<sub>ERASEALL</sub> The CPU is halted if the CPU executes code from the flash while the NVMC performs the erase operation.

## 4.3.6 Registers

| Base address | Peripheral | Instance   | Description                                   | Configuration |            |

|--------------|------------|------------|-----------------------------------------------|---------------|------------|

| 0x4001E000   | NVMC       | NVMC       | Non-volatile memory controller                |               |            |

|              |            |            | Table 5: Instances                            |               |            |

| Register     | Offset     | Descripti  | on                                            |               |            |

| READY        | 0x400      | Ready fla  | g                                             |               |            |

| CONFIG       | 0x504      | Configura  | ition register                                |               |            |

| ERASEPCR1    | 0x508      | Register f | or erasing a page in code area. Equivalent to | ERASEPAGE.    | Deprecated |

| ERASEPAGE    | 0x508      | Register f | or erasing a page in code area                |               |            |

| ERASEALL  | 0x50C | Register for erasing all non-volatile user memory                  |            |

|-----------|-------|--------------------------------------------------------------------|------------|

| ERASEPCRO | 0x510 | Register for erasing a page in code area. Equivalent to ERASEPAGE. | Deprecated |

| ERASEUICR | 0x514 | Register for erasing user information configuration registers      |            |

Table 6: Register Overview

#### 4.3.6.1 READY

Address offset: 0x400

Ready flag

| Bit number       |       | 31 30 29 28 2 | 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|-------|---------------|---------------------------------------------------------------------------|

| Id               |       |               | A                                                                         |

| Reset 0x00000000 |       | 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                   |

| Id RW Field      |       |               | Description                                                               |

| A R READY        |       |               | NVMC is ready or busy                                                     |

|                  | Busy  | 0             | NVMC is busy (ongoing write or erase operation)                           |

|                  | Ready | 1             | NVMC is ready                                                             |

#### 4.3.6.2 CONFIG

Address offset: 0x504

Configuration register

| Bit number       |     | 31 30 29 28 27 | 7 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|-----|----------------|--------------------------------------------------------------------------|

| Id               |     |                | A A                                                                      |

| Reset 0x00000000 |     | 0 0 0 0 0      | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                  |

|                  |     |                |                                                                          |

| A RW WEN         |     |                | Program memory access mode. It is strongly recommended                   |

|                  |     |                | to activate erase and write modes only when they are                     |

|                  |     |                | actively used.                                                           |

|                  | Ren | 0              | Read only access                                                         |

|                  | Wen | 1              | Write enabled                                                            |

|                  | Een | 2              | Erase enabled                                                            |

## 4.3.6.3 ERASEPCR1 ( Deprecated )

Address offset: 0x508

Register for erasing a page in code area. Equivalent to ERASEPAGE.

| Bit number       | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|---------------------------------------------------------------------------------------|

| Id               |                                                                                       |

| Reset 0x00000000 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                               |

| Id RW Field      |                                                                                       |

| A RW ERASEPCR1   | Register for erasing a page in code area. Equivalent to                               |

|                  | ERASEPAGE.                                                                            |

#### 4.3.6.4 ERASEPAGE

Address offset: 0x508

Register for erasing a page in code area

| Bit number      | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|---------------------------------------------------------------------------------------|

| Id              | A A A A A A A A A A A A A A A A A A A                                                 |

| Reset 0x0000000 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                               |

| Id RW Field     |                                                                                       |

| A RW ERASEPAGE  | Register for starting erase of a page in code area.                                   |

|                 | The value is the address to the page to be erased (addresses                          |

|                 | of first word in page). Note that the erase must be enabled                           |

|                 | using CONFIG.WEN before the page can be erased. Attempts                              |

|                 | to erase pages that are outside the code area may result in                           |

|                 | undesirable behavior, e.g. the wrong page may be erased.                              |

#### 4.3.6.5 ERASEALL

Address offset: 0x50C

Register for erasing all non-volatile user memory

| Bit number       |             | 31 30 29 28 27 26 | 5 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|-------------|-------------------|-----------------------------------------------------------------------|

| Id               |             |                   | A                                                                     |

| Reset 0x00000000 |             | 0 0 0 0 0 0       | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                               |

|                  |             |                   |                                                                       |

| A RW ERASEALL    |             |                   | Erase all non-volatile memory including UICR registers. Note          |

|                  |             |                   | that the erase must be enabled using CONFIG.WEN before                |

|                  |             |                   | the non-volatile memory can be erased.                                |

|                  | NoOperation | 0                 | No operation                                                          |

|                  | Erase       | 1                 | Start erase of chip                                                   |

#### 4.3.6.6 ERASEPCR0 (Deprecated)

Address offset: 0x510

Register for erasing a page in code area. Equivalent to ERASEPAGE.

| Bit number       | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|---------------------------------------------------------------------------------------|

| Id               |                                                                                       |

| Reset 0x00000000 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                               |

| ld RW Field      | Value Description                                                                     |

| A RW ERASEPCRO   | Register for starting erase of a page in code area. Equivalent                        |

|                  | to ERASEPAGE.                                                                         |

#### 4.3.6.7 ERASEUICR

Address offset: 0x514

Register for erasing user information configuration registers

| Bit r | numbe  | er        |             | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-------|--------|-----------|-------------|-------------------------|-----------------------------------------------------------------|

| Id    |        |           |             |                         | А                                                               |

| Res   | et OxO | 0000000   |             | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                         |

| Id    |        |           |             |                         | Description                                                     |

| А     | RW     | ERASEUICR |             |                         | Register starting erase of all user information configuration   |

|       |        |           |             |                         | registers. Note that the erase must be enabled using            |

|       |        |           |             |                         | CONFIG.WEN before the UICR can be erased.                       |

|       |        |           | NoOperation | 0                       | No operation                                                    |

|       |        |           | Erase       | 1                       | Start erase of UICR                                             |

## 4.3.7 Electrical specification

#### 4.3.7.1 Flash programming

| Symbol                   | Description                                                         | Min. | Тур. | Max. | Units |

|--------------------------|---------------------------------------------------------------------|------|------|------|-------|

| n <sub>WRITE,BLOCK</sub> | Number of writes allowed in a block before erase                    |      |      |      |       |

| n <sub>WRITE</sub>       | Number of times an address can be written before erase <sup>2</sup> |      |      |      |       |

| n <sub>ENDURANCE</sub>   | Write/erase cycles                                                  |      |      |      |       |

| t <sub>WRITE</sub>       | Time to write one 32-bit word                                       |      |      |      | μs    |

| t <sub>erasepage</sub>   | Time to erase one page                                              |      |      |      | ms    |

| t <sub>ERASEALL</sub>    | Time to erase all flash                                             |      |      |      | ms    |

$^2\,$  The page must be erased when either  $n_{\text{WRITE,BLOCK}}\, \text{or}\,\, n_{\text{WRITE}}$  is exceeded.

# 4.4 FICR — Factory information configuration registers

Factory information configuration registers (FICR) are pre-programmed in factory and cannot be erased by the user. These registers contain chip-specific information and configuration.

## 4.4.1 Registers

| Base address   | Peripheral | Instance | Description                              | Configuration |

|----------------|------------|----------|------------------------------------------|---------------|

| 0x10000000     | FICR       | FICR     | Factory information configuration        |               |

|                |            |          |                                          |               |

|                |            |          | Table 7: Instances                       |               |

|                |            |          |                                          |               |

| Register       | Offset     | Descrip  | tion                                     |               |

| CODEPAGESIZE   | 0x010      | Code m   | emory page size                          |               |

| CODESIZE       | 0x014      | Code m   | emory size                               |               |

| DEVICEID[0]    | 0x060      | Device i | dentifier                                |               |

| DEVICEID[1]    | 0x064      | Device i | dentifier                                |               |

| ER[0]          | 0x080      | Encrypt  | ion root, word 0                         |               |

| ER[1]          | 0x084      | Encrypt  | ion root, word 1                         |               |

| ER[2]          | 0x088      | Encrypt  | ion root, word 2                         |               |

| ER[3]          | 0x08C      | Encrypt  | ion root, word 3                         |               |

| IR[0]          | 0x090      | Identity | root, word 0                             |               |

| IR[1]          | 0x094      | Identity | root, word 1                             |               |

| IR[2]          | 0x098      | Identity | root, word 2                             |               |

| IR[3]          | 0x09C      | Identity | root, word 3                             |               |

| DEVICEADDRTYPE | 0x0A0      | Device a | address type                             |               |

| DEVICEADDR[0]  | 0x0A4      | Device   | address 0                                |               |

| DEVICEADDR[1]  | 0x0A8      | Device a | address 1                                |               |

| INFO.PART      | 0x100      | Part coo | le                                       |               |

| INFO.VARIANT   | 0x104      | Part var | iant, hardware version and production co | onfiguration  |

| INFO.PACKAGE   | 0x108      | Package  | option                                   |               |

| INFO.RAM       | 0x10C      | RAM va   | riant                                    |               |

| INFO.FLASH     | 0x110      | Flash va | iriant                                   |               |

|                | 0x114      |          |                                          | Reserved      |

|                | 0x118      |          |                                          | Reserved      |

|                | 0x11C      |          |                                          | Reserved      |

| TEMP.A0        | 0x404      | Slope d  | efinition A0                             |               |

| TEMP.A1        | 0x408      | Slope d  | efinition A1                             |               |

| TEMP.A2        | 0x40C      | Slope d  | efinition A2                             |               |

| TEMP.A3        | 0x410      | Slope d  | efinition A3                             |               |

| TEMP.A4        | 0x414      | Slope d  | efinition A4                             |               |

| TEMP.A5        | 0x418      | Slope d  | efinition A5                             |               |

| TEMP.B0        | 0x41C      | Y-interc | ept B0                                   |               |

| TEMP.B1        | 0x420      | Y-interc | ept B1                                   |               |

| TEMP.B2        | 0x424      | Y-interc | ept B2                                   |               |

| TEMP.B3        | 0x428      | Y-interc | ept B3                                   |               |

| TEMP.B4        | 0x42C      | Y-interc | ept B4                                   |               |

| TEMP.B5        | 0x430      | Y-interc | ept B5                                   |               |

| TEMP.T0        | 0x434      | Segmer   | at end TO                                |               |

| TEMP.T1        | 0x438      | Segmer   | it end T1                                |               |

| TEMP.T2        | 0x43C      | Segmer   | it end T2                                |               |

| TEMP.T3        | 0x440      | Segmer   | it end T3                                |               |

Downloaded from Arrow.com.

| Register | Offset | Description    |

|----------|--------|----------------|

| TEMP.T4  | 0x444  | Segment end T4 |

Table 8: Register Overview

#### 4.4.1.1 CODEPAGESIZE

Address offset: 0x010

Code memory page size

| Bit n | umb   | er           | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 5 24 | 1 23 | 3 22 | 2 21 | 20 | 0 19 | 18 | 17   | 16  | 15 | 14 | 13 | 12 : | 11 1 | 10 : | 9 | 8 | 7 | 6 | 5 4        | 13  | 2 | 1 | 0 |

|-------|-------|--------------|----|----|----|----|----|----|----|------|------|------|------|----|------|----|------|-----|----|----|----|------|------|------|---|---|---|---|------------|-----|---|---|---|

| Id    |       |              | А  | A  | А  | А  | A  | А  | A  | A    | А    | A    | A    | А  | A    | A  | A    | А   | А  | А  | А  | A    | A    | A    | A | A | A | A | 4 <i>4</i> | A A | A | А | A |

| Rese  | t OxO | 00001000     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0    | 0    | 0  | 0    | 0  | 0    | 0   | 0  | 0  | 0  | 1    | 0    | 0    | 0 | 0 | 0 | 0 | 0 0        | 0 0 | 0 | 0 | 0 |

| Id    |       |              |    |    |    |    |    |    |    |      |      |      |      |    |      |    |      |     |    |    |    |      |      |      |   |   |   |   |            |     |   |   |   |

| А     | R     | CODEPAGESIZE |    |    |    |    |    |    |    |      | С    | ode  | m    | em | ory  | pa | ge s | ize |    |    |    |      |      |      |   |   |   |   |            |     |   |   |   |

#### 4.4.1.2 CODESIZE

Address offset: 0x014

Code memory size

| Bit r | numl  | ber      | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 2 | 22 2 | 12  | 0 19 | 9 18 | 3 17 | 16  | 15  | 14 1  | 3 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 4 | 4 3        | 3 2 | 1 | 0 |

|-------|-------|----------|----|----|----|----|----|----|----|----|------|------|-----|------|------|------|-----|-----|-------|------|----|----|---|---|---|---|-----|------------|-----|---|---|

| Id    |       |          | A  | А  | А  | А  | А  | A  | А  | A  | A    | A A  | 4 ۸ | A A  | A    | А    | А   | А   | A     | A A  | А  | А  | А | А | А | A | A   | 4 <i>4</i> | A A | A | А |

| Res   | et Ox | 00000030 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0 0  | ) ( | 0 0  | 0    | 0    | 0   | 0   | 0 (   | 0 0  | 0  | 0  | 0 | 0 | 0 | 0 | 1 : | 1 (        | 0   | 0 | 0 |

| Id    |       |          |    |    |    |    |    |    |    |    | Des  |      |     |      |      |      |     |     |       |      |    |    |   |   |   |   |     |            |     |   |   |

| A     | R     | CODESIZE |    |    |    |    |    |    |    |    | Coc  | le m | en  | nory | siz  | e in | nur | nbe | er of | pag  | es |    |   |   |   |   |     |            |     |   |   |

Total code space is: CODEPAGESIZE \* CODESIZE

#### 4.4.1.3 DEVICEID[0]

Address offset: 0x060

Device identifier

| A R DEVICEID     | 64 bit unique                          | e device identifier                    |           |

|------------------|----------------------------------------|----------------------------------------|-----------|

|                  |                                        |                                        |           |

| Reset 0xFFFFFFFF | 1 1 1 1 1 1 1 1 1 1 1 1 1 1            | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1        | 1 1 1 1 1 |

| Id               | A A A A A A A A A A A A A A A A A A A  | A A A A A A A A A A A A A A A A        | A A A A A |

| Bit number       | 31 30 29 28 27 26 25 24 23 22 21 20 19 | 9 18 17 16 15 14 13 12 11 10 9 8 7 6 5 | 4 3 2 1 0 |

DEVICEID[0] contains the least significant bits of the device identifier. DEVICEID[1] contains the most significant bits of the device identifier.

#### 4.4.1.4 DEVICEID[1]

Address offset: 0x064 Device identifier

|                  | 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|-------------------------|---------------------------------------------------------------|

| Id ,             | A A A A A A A           | A A A A A A A A A A A A A A A A A A A                         |

| Reset 0xFFFFFFFF | 1 1 1 1 1 1 1 1         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                       |

|                  |                         | Description                                                   |

| A R DEVICEID     |                         | 64 bit unique device identifier                               |

DEVICEID[0] contains the least significant bits of the device identifier. DEVICEID[1] contains the most significant bits of the device identifier.

## 4.4.1.5 ER[0]

Address offset: 0x080

Encryption root, word 0

| Id RW Field      | Value Id | Value               | Description Encryption root, word n                              |

|------------------|----------|---------------------|------------------------------------------------------------------|

| Reset 0xFFFFFFFF |          |                     | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                          |

| Id               |          | АААААА              | A A A A A A A A A A A A A A A A A A A                            |

| Bit number       |          | 31 30 29 28 27 26 2 | 5 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

#### 4.4.1.6 ER[1]

Address offset: 0x084

Encryption root, word 1

| Bit number           | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|----------------------|---------------------------------------------------------------------------------------|

| Id                   | A A A A A A A A A A A A A A A A A A A                                                 |

| Reset 0xFFFFFFF      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                               |

| Id RW Field Value Id | Value Description                                                                     |

| A R ER               | Encryption root, word n                                                               |

#### 4.4.1.7 ER[2]

Address offset: 0x088

Encryption root, word 2

| Bit number       | 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|----------------------|------------------------------------------------------------------|

| Id               | ААААААА              |                                                                  |

| Reset 0xFFFFFFFF | 1 1 1 1 1 1 1        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                          |

| Id RW Field      |                      | Description                                                      |

| A R ER           |                      | Encryption root, word n                                          |

#### 4.4.1.8 ER[3]

Address offset: 0x08C

Encryption root, word 3

| Bit number       | 31 30 29 28 27 26 | 6 25 24 23 22 21 20 19 18 | 17 16 15 14 13 12 11 | 10 9 8 7 6 5 | 4 3 2 1 0 |

|------------------|-------------------|---------------------------|----------------------|--------------|-----------|

| Id               | АААААА            |                           | AAAAAA               | AAAAAA       | AAAAA     |

| Reset 0xFFFFFFFF | 1 1 1 1 1 1       | 1 1 1 1 1 1 1 1           | 1 1 1 1 1 1 1        | 1 1 1 1 1 1  | 1 1 1 1 1 |

| Id RW Field      |                   |                           |                      |              |           |

| A R ER           |                   | Encryption root, w        | vord n               |              |           |

#### 4.4.1.9 IR[0]

Address offset: 0x090

Identity root, word 0

| Bit number       31 30 29 28 27 26 25 24 23 22 12 0 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0         Id       A A A A A A A A A A A A A A A A A A A | A R IR               |                   | Identity root, word n                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|---------------------------------------------------------------------|

| Id AAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA                                                                                                                      | Id RW Field Value Id |                   | Description                                                         |

|                                                                                                                                                              | Reset 0xFFFFFFFF     | 1 1 1 1 1 1       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                             |

| Bit number 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                                             | Id                   | ΑΑΑΑΑ             | A A A A A A A A A A A A A A A A A A A                               |

|                                                                                                                                                              | Bit number           | 31 30 29 28 27 26 | 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

#### 4.4.1.10 IR[1]

Address offset: 0x094

Identity root, word 1

| Bit number           | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|----------------------|---------------------------------------------------------------------------------------|

| Id                   |                                                                                       |

| Reset 0xFFFFFFF      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                               |

| Id RW Field Value Id | Value Description                                                                     |

| A R IR               | ldentity root, word n                                                                 |

#### 4.4.1.11 IR[2]

Address offset: 0x098 Identity root, word 2

| Bit number      | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 | 1 0 |

|-----------------|-----------------------------------------------------------------------------------|-----|

| Id              |                                                                                   | A A |

| Reset 0xFFFFFFF | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                           | 1 1 |

| Id RW Field     |                                                                                   |     |

| A R IR          | Identity root, word n                                                             |     |

## 4.4.1.12 IR[3]

Address offset: 0x09C

Identity root, word 3

| Bit number           | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

|----------------------|-------------------------------------------------------------------------------------|

| Id                   | A A A A A A A A A A A A A A A A A A A                                               |

| Reset 0xFFFFFFF      | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                             |

| Id RW Field Value Id | Value Description                                                                   |

|                      |                                                                                     |

#### 4.4.1.13 DEVICEADDRTYPE

#### Address offset: 0x0A0

Device address type

| Bit numbe  | r              |        | 31 30 29 28 27 26 25 24 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------|----------------|--------|-------------------------|------------------------------------------------------------------|

| Id         |                |        |                         | А                                                                |

| Reset 0xFF | FFFFFF         |        | 1 1 1 1 1 1 1 1         | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                          |

| Id RW      |                |        |                         | Description                                                      |

| A R        | DEVICEADDRTYPE |        |                         | Device address type                                              |

|            |                | Public | 0                       | Public address                                                   |

|            |                | Random | 1                       | Random address                                                   |

#### 4.4.1.14 DEVICEADDR[0]

Address offset: 0x0A4

Device address 0

| Bit number       | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|---------------------------------------------------------------------------------------|

| Id               |                                                                                       |

| Reset 0xFFFFFFFF | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                               |

| Id RW Field      | Value Description                                                                     |

| A R DEVICEADDR   | 48 bit device address                                                                 |

|                  | DEVICEADDR[0] contains the least significant bits of                                  |

|                  | the device address. DEVICEADDR[1] contains the most                                   |

|                  | significant bits of the device address. Only bits [15:0] of                           |

|                  | DEVICEADDR[1] are used.                                                               |

## 4.4.1.15 DEVICEADDR[1]

Address offset: 0x0A8

Device address 1

| Bit number      | 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|-----------------|---------------------------------------------------------------------------------------|

| Id              |                                                                                       |

| Reset 0xFFFFFFF | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                               |

| Id RW Field     |                                                                                       |

| A R DEVICEADDR  | 48 bit device address                                                                 |

|                 | DEVICEADDR[0] contains the least significant bits of                                  |

|                 | the device address. DEVICEADDR[1] contains the most                                   |

|                 | significant bits of the device address. Only bits [15:0] of                           |

|                 | DEVICEADDR[1] are used.                                                               |

|                 | DEVICEADDR[1] are used.                                                               |

#### 4.4.1.16 INFO.PART

Address offset: 0x100 Part code

| Bit number       |        | 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 1 | 16 15 14 13 12 | 11 10 9 8 7 | 6543210 |

|------------------|--------|-------------------------|------------------------|----------------|-------------|---------|

| Id               |        | A A A A A A A A         | A A A A A A A A        | ААААА          | AAAAA       |         |

| Reset 0x00052810 |        | 0 0 0 0 0 0 0 0         | 0000010                | 1 0 0 1 0      | 1 0 0 0 0   | 0010000 |

| Id RW Field      |        |                         |                        |                |             |         |

| A R PART         |        |                         | Part code              |                |             |         |

|                  | N52810 | 0x52810                 | nRF52810               |                |             |         |

|                  |        |                         |                        |                |             |         |

#### 4.4.1.17 INFO.VARIANT

#### Address offset: 0x104

Part variant, hardware version and production configuration

| Biti | numb   | er      |             | 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------|--------|---------|-------------|----------------------|------------------------------------------------------------------|

| Id   |        |         |             | ААААААА              | A A A A A A A A A A A A A A A A A A A                            |

| Res  | et Oxl | FFFFFFF |             | 1 1 1 1 1 1 1        | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                          |

| Id   |        |         |             |                      | Description                                                      |

| А    | R      | VARIANT |             |                      | Part variant, hardware version and production configuration,     |

|      |        |         |             |                      | encoded as ASCII                                                 |

|      |        |         | AAAA        | 0x41414141           | ΑΑΑΑ                                                             |

|      |        |         | AAA0        | 0x41414130           | AAAO                                                             |

|      |        |         | AABA        | 0x41414241           | AABA                                                             |

|      |        |         | AABB        | 0x41414242           | AABB                                                             |

|      |        |         | AAB0        | 0x41414230           | AABO                                                             |

|      |        |         | AACA        | 0x41414341           | AACA                                                             |

|      |        |         | AACB        | 0x41414342           | AACB                                                             |

|      |        |         | AAC0        | 0x41414330           | AACO                                                             |

|      |        |         | Unspecified | OxFFFFFFF            | Unspecified                                                      |

|      |        |         |             |                      |                                                                  |

#### 4.4.1.18 INFO.PACKAGE

#### Address offset: 0x108

Package option

| Bit number      |          | 31 30 29 28 27 26 25 24 | 4 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |

|-----------------|----------|-------------------------|---------------------------------------------------------------|

| Id              |          | A A A A A A A           |                                                               |

| Reset 0xFFFFFFF |          | 1 1 1 1 1 1 1 1         | . 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                       |

| Id RW Field     |          |                         |                                                               |

|                 |          |                         |                                                               |

| A R PACKAGE     |          |                         | Package option                                                |

| A R PACKAGE     | QF       | 0x2000                  | Package option<br>QFxx - 48-pin QFN                           |

| A R PACKAGE     | QF<br>QC |                         |                                                               |

#### 4.4.1.19 INFO.RAM

Address offset: 0x10C

RAM variant

| Bit number       |     | 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|------------------|-----|----------------------|------------------------------------------------------------------|

| Id               |     | ААААААА              | A A A A A A A A A A A A A A A A A A A                            |

| Reset 0x00000018 |     | 0 0 0 0 0 0 0        | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                          |

| Id RW Field      |     |                      |                                                                  |

| A R RAM          |     |                      | RAM variant                                                      |

|                  | K24 | 0x18                 | 24 kByte RAM                                                     |

|                  |     |                      |                                                                  |

#### 4.4.1.20 INFO.FLASH

#### Address offset: 0x110

Flash variant

| Bit number           | 31 30 29 28 27 26 25 24 | 23       22       21       20       19       18       17       16       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0 |

|----------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Id                   | A A A A A A A           |                                                                                                                                                                                                         |

| Reset 0x000000C0     | 0 0 0 0 0 0 0 0         | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0                                                                                                                                                         |

| Id RW Field Value Id |                         | Description                                                                                                                                                                                             |

| A R FLASH            |                         | Flash variant                                                                                                                                                                                           |

| К192                 | 0xC0                    | 192 kByte flash                                                                                                                                                                                         |

| Unspecified          | OxFFFFFFF               | Unspecified                                                                                                                                                                                             |

#### 4.4.1.21 TEMP.A0

Address offset: 0x404

Slope definition A0

| Bit number       | 31 30 29 28 27 | 26 25 24 23 22 21 20 19 1 | .8 17 16 15 14 13 12 | 2 11 10 9 | 8 7 | 76  | 54  | 3 | 2 1 0 |

|------------------|----------------|---------------------------|----------------------|-----------|-----|-----|-----|---|-------|

| Id               |                |                           |                      | AAA       | AA  | A A | A A | A | A A A |

| Reset 0x00000320 | 0 0 0 0 0      | 0 0 0 0 0 0 0 0           |                      | 001       | 1 ( | 0 0 | 1 0 | 0 | 000   |

| Id RW Field      |                |                           |                      |           |     |     |     |   |       |

| A R A            |                | A (slope definitio        | on) register         |           |     |     |     |   |       |

#### 4.4.1.22 TEMP.A1

Address offset: 0x408

Slope definition A1

| Bit number       | 31 30 29 28 27 | 26 25 24 23 22 21 20 1 | 9 18 17 16    | 15 14 13 1 | 2 11 10 | 98  | 7 ( | 55  | 4 | 32  | 1 0 |